RTL Design, Verification, GLS, SystemC and AMS

Expertise in Front-end RTL design and SoC integration of multi-million gates IPs and SoCs for a variety of industry verticals like mobile, processors, networking and multimedia. Experience in the design verification involving standardized methodology like UVM based functional and formal techniques, VIP development, Equivalence checking and Gate level simulations of complex IP and SoC designs.

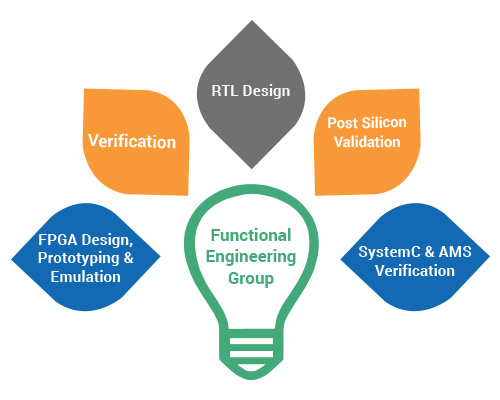

FUNCTIONAL ENGINEERING

The Functional Engineering Group at Mirafra provides design services and solutions to some of the biggest names in the global semiconductor industry in the areas of RTL & FPGA Design, Design Verification, Gate Level Simulation, Emulation, Post Silicon Validation, AMS Verification and SystemC Modelling.

With a strong legacy of more than 11 years in the industry, and with the rich experience of having worked with a majority of the Fortune-500 companies across the globe on the above mentioned technology verticals, we are ideally placed to take any design idea/architecture from concept to netlist, and further perform post silicon validation of the same.

With engineers of varying levels of experience in each of the above-mentioned verticals, and with technical leads to drive, monitor and deliver results, our commitment to quality of deliverables will continue to be at the levels that have made Mirafra stand out in the industry.

The engineers in the functional engineering group have hands-on experience on the latest technologies, methodologies, languages and techniques used in the industry. We are one of the few, if not the only, service companies that has full time training faculty and labs to enable our engineers to be at their best when working on client projects.

More information on the different technology offerings, areas of expertise, domain knowledge, methodology knowledge etc. can be found in this section. You could also go through this website to look at the various business models that we offer to our customers. These have been created with the aim of providing flexibility and multiple options that our customers can choose from.

With engineers of varying levels of experience in each of the above-mentioned verticals, and with technical leads to drive, monitor and deliver results, our commitment to quality of deliverables will continue to be at the levels that have made Mirafra stand out in the industry.

The engineers in the functional engineering group have hands-on experience on the latest technologies, methodologies, languages and techniques used in the industry. We are one of the few, if not the only, service companies that has full time training faculty and labs to enable our engineers to be at their best when working on client projects.

More information on the different technology offerings, areas of expertise, domain knowledge, methodology knowledge etc. can be found in this section. You could also go through this website to look at the various business models that we offer to our customers. These have been created with the aim of providing flexibility and multiple options that our customers can choose from.

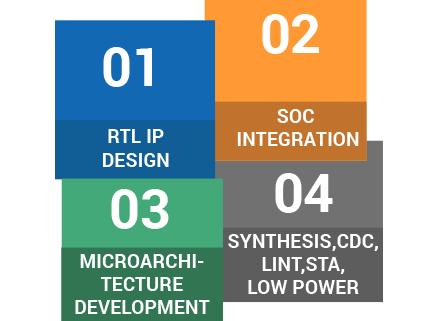

RTL DESIGN

Our team of experienced design engineers, complemented by a group of mid-level engineers have worked on multiple aspects of the RTL design flow on chips used in the automotive, mobile, networking, multimedia and processor industries. The following schematic demonstrates how Mirafra’s expertise helps the pieces of the jigsaw fall into place.

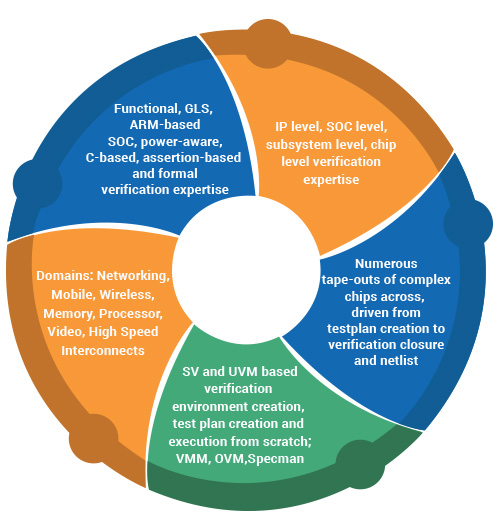

VERIFICATION

Mirafra’s verification team has proven expertise on taking complete ownership of verification of a design from scratch – whether that is an IP/SOC/subsystem – and taking it to verification closure by performing the following activities:

- Understanding the design specification document and creating the test plan

- Creating the complete verification environment using industry standard methodologies like UVM/OVM/VMM

- Executing the test plan by using an intelligent mix of constraint random, directed and random test cases

- Gate level simulations

- Verification closure through corner case verification, coverage closure and regression closure

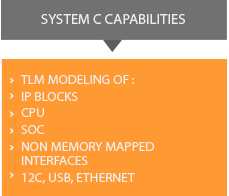

SYSTEMC VERIFICATION

Mirafra has a small but capable team with hands-on expertise in various aspects of the chip design flow where SystemC plays a critical role. They are represented in the chart below.

ANALOG & MIXED SIGNAL VERIFICATION

The AMS verification team at Mirafra has the skillsets required to execute on:

- Analog/mixed-signal block simulations

- Modelling of analog and mixed signal blocks using Verilog-AMS

- Creating digital mixed signal test benches

- Comprehensive AMS full chip verification of mixed signal ASICs.

CASE STUDIES

To portray our enormous industry experience in this area, here are few case studies. To know more, feel free to contact us.