Analog Design & Layout Std. Cells, Memories and IOs

Expertise in Layout of analog components like ADC, DAC, PLL, Bandgap, Power regulators etc. Experience in designing standard cell libraries that meet several design criteria like optimal area, power, timing etc. on several technology nodes. Specialists in high speed high density memories and associated modules. In depth understanding of design of IO cells and interfaces having unique

electrical and noise specifications.

ANALOG & MIXED SIGNAL ENGINEERING

Our team has in-depth expertise on variety of IPs such as SerDes (10, 16, 30 & 56 Gbps), DDRphy, USB 2.0, MIPIphy and Power management. We have also handled expanded portfolios of Data converters, clock circuits such as PLL, DLL & oscillators, Regulators, Bias, Bandgap references, Temperature sensors, UVLOs etc in almost all leading foundries at technologies varying from 500nm BCD to 7nm Finfet. Multiple full chip and IP level tape out has been successfully done with first pass silicon.

What sets us unique is that the knowledge gained is shared among other team members across sites to close the skill gap at any experience level.

- IP solutions

- Data converters

- Clock circuits

- Regulators

- Band-gap and other critical circuit.

STANDARD CELL SOLUTIONS

In the past, our team has delivered multiple std cell libraries at 90nm, 65nm, 45nm, 32nm, 28nm, 20nm, 16FF, 14nm, 10nm etc with leading foundries. These libraries include High performance, High density, 11T, 9T, 7.5T, 6T design. We are also expert when it comes to migration of libraries to latest technologies.

- Std cell library development.

- Process migration for older libraries

- Std cell Characterization.

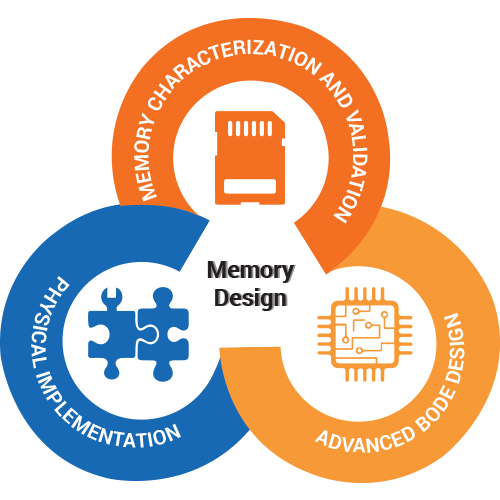

MEMORY SOLUTIONS

Wide range of memory with variety of architecture with top semiconductor companies has been done before. These includes Multi port memories, SRAM, Memory compilers, Register files & custom memories on cutting edge technologies.

- Multi-port Memory design & layout.

- Memory compilers and Register files.

- Memory Characterization.

IO SOLUTIONS

Our team has delivered IO layout from 250nm to 16nm technologies. These includes GPIOs, LVCMOS, LVTTL, LVDS, DDR etc with Analog/Power ring. ESD resuirements for HBM, MM, CDM were taken care.

- IO Libraries design, layout & Char.

- ESD and Ring design to meet ESD requirements.

MISCELLANEOUS

AMS verification for latest IPs has been done with leading simulators at multiple technologies with variety of customers.

- AMS verification

- Circuit simulations.

SERVICES

Menu